# Graphene Field-Effect **Transistors Based on Boron–Nitride Dielectrics**

*In this paper, the authors explore the use of hexagonal boron nitride as a dielectric* material in graphene devices. They show that the performance of such devices is considerably improved compared to the ones using conventional dielectrics.

By Inanc Meric, Cory R. Dean, Nicholas Petrone, Lei Wang, James Hone, PHILIP KIM, AND KENNETH L. SHEPARD, Fellow IEEE

ABSTRACT | Two-dimensional atomic sheets of graphene represent a new class of nanoscale materials with potential applications in electronics. However, exploiting the intrinsic characteristics of graphene devices has been problematic due to impurities and disorder in the surrounding dielectric and graphene/dielectric interfaces. Recent advancements in fabricating graphene heterostructures by alternately layering graphene with crystalline hexagonal boron nitride (hBN), its insulating isomorph, have led to an order of magnitude improvement in graphene device quality. Here, recent developments in graphene devices utilizing boron-nitride dielectrics are reviewed. Field-effect transistor (FET) characteristics of these systems at high bias are examined. Additionally, existing challenges in material synthesis and fabrication and the potential of graphene/BN heterostructures for novel electronic applications are discussed.

**KEYWORDS** | Graphene field-effect transistors (GFETs); hexagonal boron nitride (hBN)

## I. INTRODUCTION

For the past several decades, aggressive scaling of siliconbased technologies has enabled a steady exponential growth in semiconductor device performance, following the predications of Moore's law. Further device scaling cannot continue indefinitely, and it is predicted that in only a few years a fundamental small-scale limit in device architecture will be reached. This rapidly approaching end has animated an intensive search for novel channel materials that can outperform state-of-the-art silicon. Among these, graphene, a 2-D sheet of carbon atoms arranged in a honeycomb lattice, has attracted significant attention. Its atomically thin structure, high mechanical strength, high mechanical flexibility, high thermal conductivity, optical transparency, and potential low cost, in conjunction with its superior intrinsic carrier velocities, has made graphene attractive as a promising new material for a wide range of applications [1]–[5].

The 2-D nature of graphene means that injected charge carriers are confined to a surface just one atom thick ( $\sim$ 0.3 nm). In principal, this alone may allow graphene-based devices to push the limits of device scaling beyond those of silicon by enabling improved gate control and, therefore, reduced short channel effects in ultrashort channel devices. However, the extreme confinement means that charge carriers are also directly exposed to the surrounding environment, making transport through graphene highly sensitive to scattering from extrinsic impurities. This sensitivity has presented a serious

Manuscript received July 08, 2012; revised February 26, 2013; accepted March 25, 2013. Date of publication May 14, 2013; date of current version June 14, 2013. This work was supported by the Air Force of Scientific Research (AFOSR) Multidisciplinary University Research Initiative (MURI) Program on new graphene materials technology under Grant FA9550-09-1-0705 and by the Defense Advanced Research Projects Agency (DARPA) under U.S. Office of Naval Research Contract N00014-1210814.

I. Meric and K. L. Shepard are with the Department of Electrical Engineering, Columbia University, New York, NY 10027 USA (e-mail: shepard@ee.columbia.edu). C. R. Dean was with the Department of Electrical Engineering and the Department of Mechanical Engineering, Columbia University, New York, NY 10027 USA. He is now with the Department of Physics, The City College of New York, New York, NY 10031 USA. N. Petrone, L. Wang, and J. Hone are with the Department of Mechanical Engineering, Columbia University, New York, NY 10027 USA.

P. Kim is with the Department of Physics, Columbia University, New York,

Digital Object Identifier: 10.1109/JPROC.2013.2257634

engineering challenge to realizing high-performance devices that take full advantage of graphene's intrinsic qualities.

Graphene has no native oxide layer and instead presents a chemically inert surface with no open bonds, making it difficult to integrate dielectric passivation without chemically altering the graphene surface and degrading the transport properties of the graphene channel. The fundamental challenge in the development of graphene field-effect transistors (GFETs) has, therefore, been engineering a dielectric interface that provides optimal capacitive coupling to the gate, while also minimizing degradation of device performance.

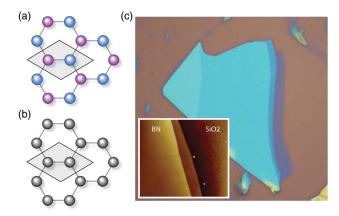

In an effort to meet these challenges, hexagonal boron nitride (hBN) has emerged as an exceptional dielectric for GFET application. hBN is a wide bandgap semiconductor (5.97 eV) [6], sharing the same layered-hexagonal crystal structure as graphite but with boron and nitrogen atoms occupying the A and B sublattices in the Bernal structure. The strong in-plane bonding of the hexagonal structure (with only 1.7% lattice mismatch to graphene [7]) makes the surface free of dangling bonds and, thus, chemically inert, presenting a nearly ideal dielectric interface to graphene (Fig. 1). Indeed, devices fabricated on hBN substrates are found to exhibit an order-of-magnitude improvement in device mobility, reduced carrier inhomogeneity, lower extrinsic doping, reduced chemical reactivity, and improved high-bias performance in comparison to devices fabricated with conventional oxide dielectrics. The dielectric properties of hBN ( $\epsilon \sim$  4 and  $V_{\rm Breakdown} \sim$ 0.7 V/nm) compare favorably with SiO<sub>2</sub> [8], [9], and the excellent thermal conductivity of hBN [10], 600-times higher than silicon dioxide, is advantageous for FET applications to improve heat dissipation.

Fig. 1. (a) hBN and (b) graphene share the same lattice structure with boron and nitrogen replacing the carbon atoms in the unit cell (the unit cell is highlighted in each by the shaded region). (c) An optical micrograph of an exfoliated hBN sample on SiO2. Inset shows an AFM image of a similar flake, showing the smooth single crystalline hBN surface. While the texture of the SiO<sub>2</sub> surface is visibly apparent, the hBN is approximately three times less rough.

In this paper, we review the latest developments in layered graphene/hBN heterostructures and discuss the role that this improved dielectric is expected to play in enabling high-frequency analog GFET applications. We begin by first reviewing the state-of-the-art GFETs fabricated with conventional oxide dielectrics, demonstrating the shortcomings of these dielectrics in conjunction with graphene. Next, we review recently developed techniques that have enabled fabrication of graphene/hBN structures without the need for conventional oxide dielectrics. We then review direct current (dc) measurements of hBN supported GFETs with particular emphasis on the improved transistor current-voltage characteristics observed in short-channel devices. We compare RF measurements performed on hBN-supported structures with highfrequency devices fabricated with conventional dielectrics. We then discuss the possible role a bandgap may play in improving RF performance. Finally, we outline the current status of extending the fabrication of high-performance graphene FETs and graphene-based heterostructure FETs to the wafer scale.

# II. GRAPHENE TRANSISTORS BASED ON CONVENTIONAL OXIDE DIELECTRICS

Graphene bandstructure is characterized by a linear dispersion near the symmetry points where the valence and conduction bands touch. At the charge neutrality point (CNP), where the bands cross, local impurities form an inhomogeneous network of spatially segregated electron and hole puddles. Therefore, even in undoped graphene, these potential fluctuations result in residual conduction paths, which limit the achievable minimum conductivity at the CNP. At ambient temperatures, this inhomogeneous charge network is "smeared out" giving rise to a sizable minimum conductivity at the CNP. This limits the ON/OFF current ratio achievable in graphene to the order of 10 in the cleanest devices, making graphene impractical for use in digital applications where typical ON/OFF ratios of greater than 10<sup>4</sup> are desired for logic operation [11]. For intrinsic graphene, where room temperature transport is limited only by scattering off of internal phonon modes, the electron drift velocity is predicted to be greater than  $4 \times 10^7$  cm/s [12], nearly four times larger than in Si. The main interest in graphene electronics, therefore, lies in high-frequency analog transistor applications where a bandgap is not required and the short transit times could enable power gain at frequencies exceeding 1 THz [13], [14].

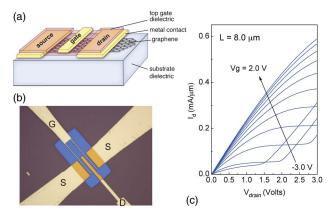

GFET devices are typically fabricated on SiO<sub>2</sub>supported graphene. Alternative substrates such as SiC [16] have been utilized; however, in all cases, a local gate is required for high-bias operation. In order to accomplish this, an oxide dielectric is typically deposited onto the top surface of the graphene sheet followed by evaporation of a top metal gate [Fig. 2(a)]. The top-gate dielectric requires

Fig. 2. (a) Schematic of a generic GFET construction. Typically, an oxide layer is deposited onto the top graphene surface to enable deposition of a local top gate. (b) An optical micrograph of a GFET fabricated in a  $\pi$ -gate structure to allow high-frequency characterization similar to [15]. (c) I-V characteristics of a 8- $\mu$ m-long GFET showing current saturation and the characteristic "kink."

an initial deposition of a noncovalent functionalization layer adsorbed on the graphene surface, such as a thin layer of oxidized aluminum or a polymer layer [17]-[19] in order to promote adhesion. In these devices, performance is limited not by the graphene itself, but rather by the chemically active buffer layer and oxide surfaces which trap charged impurities at the graphene interfaces, introduce dopants and Coulomb scatterers, impart roughness to the graphene sheet, and ultimately limit transport mobility and produce hysteretic current-voltage characteristics.

Despite these limitations, GFETs are shown to have respectable I-V characteristics at long channel lengths and impressive high-frequency performance at short channel lengths. Fig. 2(c) shows the typical saturating I-V characteristics of a 8-\mu m-long GFET associated with a unipolar channel. The observed current saturation is attributed to velocity saturation due to coupling to optical phonon modes. Under specific combinations of drain and gate biasing, the channel can be rendered ambipolar, resulting in a pronounced "kink" in the curves [21]. This is produced by the vanishing carrier density at the drain end as the CNP enters the channel with reduced gate-todrain potential, rendering the current in the channel relatively insensitive to  $V_{\text{drain}}$ . By increasing the drain bias beyond the kink, the CNP moves further into the channel, and the opposite type of carriers is introduced into the channel from the drain. In this ambipolar regime, the CNP becomes a place of recombination for holes and electrons.

The radio-frequency (RF) performance of field-effect transistors (FETs) is usually quantified by the cutoff frequency  $f_T$  and the maximum oscillation frequency  $f_{\text{max}}$ , which correspond to the frequencies at which the shortcircuit current gain and maximum available power gain, respectively, roll off to unity. Intrinsic  $f_T$  (one that does not include the effects of device parasitics) is given by

$$f_T = \frac{g_m}{2\pi C_g} \tag{1}$$

where  $g_m$  is the transconductance and  $C_g$  is the gate capacitance. In the standard short-channel semiconductor model where current saturation at high source-drain bias results from saturation of the carrier velocity, leaves  $f_T \propto v_{\rm sat}/L$ , where  $v_{\rm sat}$  is the saturation velocity and L is the channel length. For silicon complementary metaloxide-semiconductor (CMOS), in which devices are scaled to the ballistic limit, this saturation velocity is determined by the carrier source injection velocity [22]. Maximizing  $f_T$  comes from enhancing  $v_{sat}$  and minimizing L. Indeed, intrinsic  $f_T$  values larger than 420 GHz for GFETs with conventional oxide dielectrics have been demonstrated by scaling the channel length to sub-100 nm [23]. However, RF measurements have generally been reported for top-gated device structures whose currentvoltage characteristics do not show strong current saturation due to relatively poor gate-oxide interfaces or weak gate coupling [15], [16], [24]-[27]. As a result, device output conductance is high, power gain is limited, and the maximum oscillation frequency  $(f_{\text{max}})$  is typically only one-tenth of  $f_T$  [28].

$f_{\rm max}$  is generally the more important figure of merit for analog applications as power gain determines the ultimate utility of the device.  $f_{\text{max}}$  depends much more critically on certain parasitics such as gate resistance, and device characteristics, such as output resistance, than does  $f_T$ .  $f_{max}$ performance can be improved with device structures that show better current saturation and T-gate structures that reduce gate resistance.

Contact resistance directly degrades  $g_m$  and, therefore, has an effect on both  $f_T$  and  $f_{\text{max}}$ . Realizing good contact resistance to graphene has long been problematic, with values reported in the literature ranging from  $\sim$ 100  $\Omega\mu$ m to more than 1 k $\Omega\mu$ m. These values are 10–100 times larger than what is achieved in Si devices. Contact resistance effects become even more pronounced in shortchannel devices as the relative contribution to the total device resistance increases.

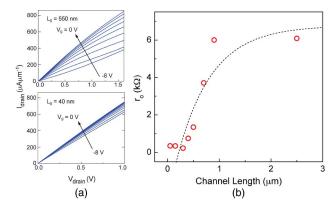

While GFETs based on oxide dielectrics with device lengths of a few micrometers show good saturation, output resistance diminishes for devices scaled below a micrometer (Fig. 3). A recent study identified mobile trapped charges in these surrounding dielectrics as the reason behind the triode-like characteristics for short channel devices. Using a pulsed measurement approach to measure dc response on time scales shorter than the response time of the traps, full saturation is recovered in devices with channel lengths down to 140 nm [19]. Output

Fig. 3. Channel length scaling in GFETs fabricated with conventional oxide dielectrics. At short channel lengths, the high bias characteristics are substantially diminished, exhibiting practically no saturation for sub-100-nm devices. The two plots in (a) show I-V curves of devices fabricated from CVD-grown graphene with 550-nm (upper panel) and 40-nm (lower panel) gate lengths [20]. (b) Peak output resistance versus channel length measured from several exfoliated devices with a HfO2 top gate dielectric (unpublished). Data are shown for the bias condition that results in the maximum output resistance. Dashed line is a guide to the eye highlighting the dramatic decrease in r. at short channels.

conductances as low as 0.3 mS/mm in saturation were reported, suggesting that an improved dielectric in these short channel GFETs could allow significant improvement in  $f_{\text{max}}$ , and potentially eliminate the large discrepancy between  $f_{\text{max}}$  and  $f_T$  so far reported in the literature.

In spite of the impressive  $f_T$  values that have been achieved, the low mobility, low  $f_{\text{max}}$ , and nonsaturating characteristics generally reported for GFETs with conventional oxide dielectrics raise significant questions as to whether graphene-based technologies can actually outperform silicon CMOS. A further concern is the importance of band-to-band Klein tunneling in very short channel GFETs, which may prevent current saturation even in the presence of improved dielectric interfaces [14]. The use of hBN dielectric with substantially improved interface to graphene provides an opportunity to address these questions.

# III. GRAPHENE/hBN **HETEROSTRUCTURES**

#### A. Fabrication

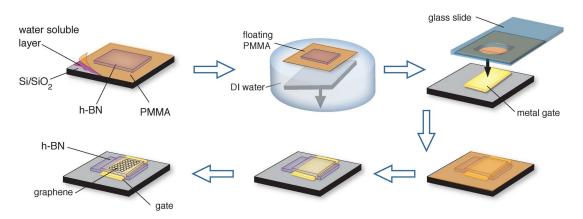

The highest purity hBN currently available is synthetically grown using a high-pressure-high-temperature (HP-HT) method [29]. This results in millimeter-size crystallites, resembling flakes of Kish graphite, which can be exfoliated down to arbitrary thicknesses, using the same techniques that have been developed for producing graphene samples of an arbitrary number of layers [30]. Using a mechanical layer-by-layer fabrication process, GFETs can be built utilizing hBN as either the top or bottom layer dielectric (or both). This mechanical layering permits integration of uniform hBN layers with thicknesses down to a single monolayer, and without the need for the adhesion layer characteristic of oxide processes. Fig. 4 shows an example of the fabrication process flow we use to realize locally gated GFETs for high-bias dc operation, similar to the fabrication process developed in [31].

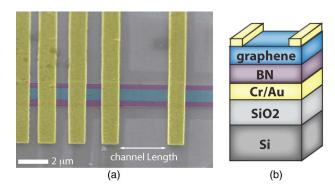

A false-colored scanning electron microscope (SEM) image of a device fabricated in this way is shown in Fig. 5. The device geometry shown here allows us to utilize the same hBN dielectric layer as both a supporting substrate and local-gate dielectric eliminating the need for an additional top gate. We note that this technique allows a variety of application-specific device architectures to be fabricated with only small variations to the process. For RF measurements, a two-finger  $(\pi)$ -gate layout is used to

Fig. 4. The mechanical transfer of both graphene and hBN starts with exfoliated hBN on top of a Si chip with a two-layer polymer coating. The water soluble bottom polymer layer is dissolved in a water bath and the polymethyl methacrylate film with the hBN remains floating on the water surface. The hBN flake is transferred onto a predefined metal gate and the polymer layer dissolved, leaving the hBN on the metal. The same steps are repeated for graphene.

Fig. 5. (a) False color SEM image showing a typical hBN-supported GFET device. (b) Cross-sectional schematic of the device shown in (a).

allow S-parameter characterization at high frequencies with coplanar microprobes. To reduce gate resistance in the RF structure, 200-nm-thick tungsten metal gates are patterned into a 1- $\mu$ m SiO<sub>2</sub> layer using a Damascene-like process, followed by a chemical-mechanical polishing (CMP) step to ensure a flat surface that exposes the gate metal surface [32].

## **B. DC Measurements**

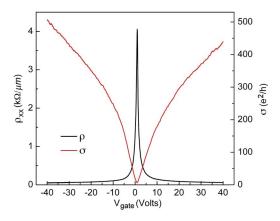

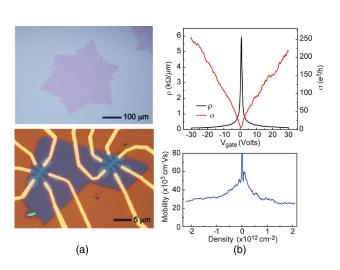

The first transport characteristics of a graphene/hBN device were reported for hBN supported heterostructures fabricated on Si/SiO2 substrates, similar to that shown in Fig. 5, but utilizing a four-terminal Hall bar design and using the doped silicon substrate as a global bottom gate [31]. In Fig. 6, the four-probe resistivity and conductivity of such a device is shown. This device shows excellent transport by several measures. The charge neutrality point (Dirac voltage), manifested as a resistivity peak, is close to zero gate voltage and has a very narrow full width at half maximum, approximately 1 V, indicating nearly a full order of magnitude less inhomogeneity than usually measured in SiO<sub>2</sub>-supported devices. The density-independent mobility extracted from the self-consistent Boltzmann equation [33] is approximately 80 000 cm<sup>2</sup>/Vs, at least a factor of three better than in the best reported SiO<sub>2</sub>-supported samples.

The improved transport of graphene/hBN heterostructures has recently also been confirmed by the measurement of ballistic transport in micrometer-long devices [35], measurement of improved temperature-dependent conductivity [38], and observation of disorder-limited physical phenomenon that previously were not observable in samples with conventional dielectrics [39], [40]. In addition, scanning tunneling microscope measurements show less inhomogeneity and surface roughness [36], [37].

The graphene/hBN FET devices also exhibit significantly enhanced high-bias characteristics [34], [41], [42], compared to GFETs fabricated with oxide dielectrics (as described in Section II) at comparable channel lengths. Using a local bottom-gated FET structure with multiple voltage probes along the length of the graphene (as shown

Fig. 6. Resistivity  $(\rho)$  and conductivity  $(\sigma)$  as a function of gate voltage for a graphene Hall-bar device on hBN at 1.6 Kelvin. The conductivity has a sublinear behavior only observed in very high mobility samples. This represents an exceptional device, with the mobility measuring  $\sim$ 80 000 cm $^2$ /Vs at high density. The mean mobility measured from over 25 samples, at the same carrier density, measures  $\sim$ 35 000 cm<sup>2</sup>/Vs.

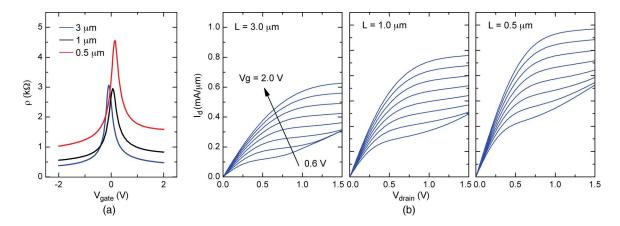

in Fig. 5) allows the fabrication of different channel length devices out of the same sample. Fig. 7(a) shows the channel resistivity  $\rho$  at small source-drain bias (1 mV) as a function of the bottom-gate voltage  $V_{\rm gate}$  for three devices with channel lengths of 3, 1, and 0.5  $\mu$ m, measured at room temperature. The low-field mobility can be extracted from the two-probe measurements by  $\mu = (1/C_g) *$  $(L/W)*(g_m/V_{ds})$ , where  $C_g$  is the gate capacitance, ~363 nF/cm<sup>2</sup> calculated from the measured hBN thickness of 8.5 nm. L and W are the device length and width, respectively, and  $g_m$  is the transconductance.

The mobility of the 3- $\mu$ m device is close to 11 000 cm<sup>2</sup>/Vs in ambient air, lower than typically reported for graphene-on-hBN Hall bar structures at cryogenic temperatures. Two-terminal measurements, however, consistently give lower mobilities when compared to fourterminal measurements, even of the same device, due to the large contribution of contact resistance to the total measured resistance. Furthermore, room temperature measurements are mostly limited by acoustic phonons, which freeze out and do not limit low-temperature transport. The CNP is at -0.07 V and the gate-voltage hysteresis is less than 10 mV, indicating that there is minimal doping of the graphene channel due to external impurities. hBNsupported devices appear to be more stable compared to other GFET types; they show unchanged characteristics after repeated measurements and demonstrate stability over the course of several months.

The I-V characteristics of three different channel length devices are shown in Fig. 7(b). All devices show current saturation as well as the kink associated with an ambipolar channel, as described in Section II. The 0.5- $\mu$ m-channel-length device shows an  $I_{\rm on}$  of more than 1 mA/ $\mu$ m. It is also important to consider the small-signal

Fig. 7. DC measurements of GFETs in ambient conditions from [34]. (a) Low-field resistance of three devices with channel lengths of 3, 1, and 0.5 µm. (b) I-V characteristics of the same three devices for gate voltage from 0.6 to 2 V in 0.2-V steps.

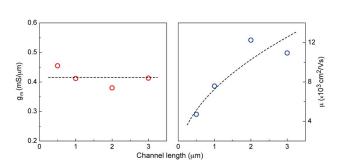

device parameters. The peak transconductance exceeds 400 mS/mm. The peak dc voltage gain  $(g_m r_o)$  for this device is larger than 46, the highest value reported so far for any graphene FET [34]. Fig. 8 shows the maximum transconductance and the low-field mobility as a function of channel length. While  $g_m$  is relatively independent of channel length, the mobility of the devices drops by more than a factor of two as channel length decreases from 3 to 0.5  $\mu$ m. Both the channel length independence of the transconductance and the change in mobility are consistent with velocity-saturation-dominated transport. The origin of the diminishing mobility with channel length is not presently understood, but this may be related to a combination of the increasing dominance of contact resistance at short channels and the difficulty in accurately determining mobility in this regime [43].

### C. RF Measurements

Of particular importance for device applications, RF measurements recently conducted on GFETs exploiting high-quality boron-nitride dielectrics demonstrate im-

Fig. 8. Channel length dependence of  $g_m$  and  $\mu$ . Peak transconductance is relatively constant with changing channel length, whereas the low-field mobility shows a decreasing trend with channel length. The dashed lines are guide to the eye.

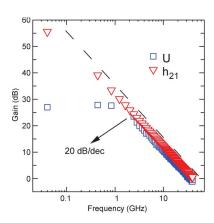

proved power gain [41], [42]. The representative RF GFET device has a  $\pi$ -gate and a ground–signal–ground coplanar waveguide layout with a channel width of approximately 38  $\mu$ m and channel length of 0.6  $\mu$ m. The transconductance of this device is 280 mS/mm, somewhat lower than the devices described in Section III-B, mainly due to channel inhomogeneity more evident at large device widths. The high-frequency measurements shown in Fig. 9 are performed to 40 GHz with a standard openshort de-embedding method [44]. The current-gain  $(h_{21})$ and unilateral power gain (U) are plotted at the bias point of peak  $g_m$ , yielding  $f_T$  and  $f_{max}$  of 44 and 34 GHz, respectively. Without de-embedding,  $f_T$  and  $f_{max}$  are 24 and 17 GHz, respectively.

Most importantly, the improved output characteristic of the hBN-supported GFETs enhances the unilateral power gain to a record value for graphene-based devices. In this relatively long-channel hBN-supported device,

Fig. 9. Current gain  $(h_{21})$  and unilateral power gain (U) after de-embedding. The  $f_T$  is 44 GHz and the  $f_{\text{max}}=$  34 GHz for this 600-nm channel-length device [41]. The dashed line follows the slope of 20 dB/decade.

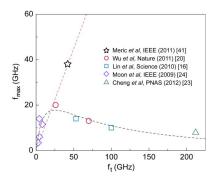

Fig. 10.  $f_{\text{max}}$  versus  $f_T$  for graphene devices reported in literature. Star indicates measurement from an hBN-supported device. All other symbols correspond to devices fabricated with conventional oxide dielectrics. Dashed black curve represents a guide to the eye for the data from oxide-based devices. Red dashed line indicates the expected scaling behavior for the hBN-supported device [41].

achievable  $f_{\text{max}}$  already outperforms oxide-dielectric-based devices that have up to ten times shorter gate lengths. We note that the  $f_{\text{max}}/f_{\text{T}}$  ratio for this device is as high as 0.86, significantly greater than the value typically observed for GFETs fabricated with oxide-based dielectrics. Fig. 10 compares the  $f_T$  and  $f_{max}$  of representative devices from the literature. The ratio of the two values is close to one for hBN devices, while for the oxide-supported GFETs the  $f_{\rm max}/f_T$  ratio is consistently less than 0.4. If current saturation can be maintained with channel-length scaling for hBN-supported devices,  $f_{\text{max}}$  values of up to 300 GHz could be achievable at 100-nm channel length [41].

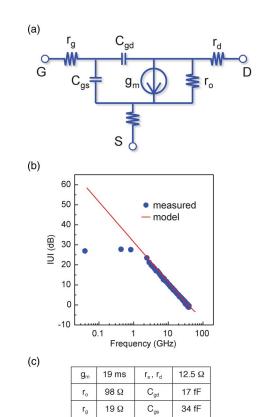

We use the small-signal-equivalent circuit in Fig. 11(a) to model the high-frequency response of the GFETs. Good agreement is obtained with the measured unilateral gain, as shown in Fig. 11(b), using the component values in Fig. 11(c). The extracted small-signal values are also in good agreement with values derived from the I-V characteristics. From these extracted values, we can also identify three significant limitations on high-frequency performance for existing GFET technologies. First, the bias point for this characterization is chosen to maximize transconductance. Because we do not have independent control of the CNP in these devices, however, this does not correspond to the bias of maximum output resistance. The value of the output resistance  $r_0$  could be increased from 100 to nearly 500  $\Omega$  through independent CNP control. Second, a significant portion of the channel capacitance is apportioned to the drain with  $C_{gd}/C_{gs}=0.5$ , significantly higher than in silicon devices. This is expected to improve with better current saturation. Finally, achieving good contacts to graphene remains problematic, as described in Section II. From the small-signal model, the contact resistance is estimated to be 950  $\Omega\mu$ m. While typical for GFETs reported in the literature, this contact resistance is more than two orders of magnitude larger than in traditional silicon devices. The  $f_{\rm max}$  of the device in Fig. 11 would be

Fig. 11. Small-signal modeling. (a) The small-signal-equivalent circuit used to model the high-frequency behavior of GFETs. (b) Unilateral power gain of both measured and modeled devices. (c) Small-signal values used in the model to obtain the fit in (b).

improved by a factor of two if the contact resistance could be reduced to 40  $\Omega\mu$ m, which is the theoretical minimum value [45].

## IV. BANDGAP

While exploiting graphene for RF applications does not require the existence of a bandgap per se, theoretical calculations indicate that inducing even a modest gap, on the order of only 100 meV, would optimize small-signal circuit performance [46]. Furthermore, a small gap could significantly improve device performance in short-channel devices by limiting band-to-band tunneling processes. This holds practical relevance since opening a bandgap in graphene is possible by several techniques.

By etching graphene into narrow "ribbons," a bandgap can be induced by lateral confinement, where the gap varies inversely with the width of the ribbon. Gaps as large as 200 meV have been achieved in graphene nanoribbons [47], and, in principle, gaps larger than 0.5 eV can be achieved for device widths less than 5 nm [48]. Fabrication of such devices remains a difficult technological challenge, particularly on the wafer scale. More problematic, carving graphene into nanoribbons by plasma etching leaves the

device edges highly disordered. In the case of ultranarrow ribbons, this edge disorder dominates transport characteristics, and mobility decreases dramatically, offsetting the potential benefits graphene may offer over silicon [49].

More generally, any process that lifts the degeneracy of the A-B sublattice will open a gap in the energy spectrum. Uniaxial strain has been proposed as one way to achieve this; however, the expected strain required to open a gap is in excess of 20%, which is technologically infeasible [50]. Alternatively, several calculations have suggested that if graphene could be epitaxially aligned to hBN, the difference in interaction energy between the carbon-boron and carbon-nitrogen atoms would open a gap as large as 50 meV [7]. To date, no experiments have been successful at controlling the crystallographic alignment in hBNsupported graphene structures, and in the several studies of graphene on hBN, no one has yet reported evidence of such a bandgap [31].

Bilayer graphene, consisting of two Bernal-stacked graphene sheets, also exhibits a gapless bandstructure intrinsically. However, application of a transverse electric displacement field breaks the layer symmetry, resulting in a gap proportional to the applied field [51]. This gatetunable bandgap is a unique feature of bilayer graphene and has generated significant technological interest, especially in the area of tunable optoelectronics. For high-frequency FET devices, the ability to induce a bandgap offers the possibility of enhancing saturation characteristics and thereby overcoming the low output resistance that so far limits  $f_{\rm max}$  in short devices. Recent high-bias measurements in a dual-gated bilayer FET indeed demonstrate enhanced voltage gain by up to a factor of six larger than similar monolayer devices [52]. In order to utilize bilayer graphene for RF applications, two outstanding issues will need to be addressed. First, bilayer devices fabricated on SiO<sub>2</sub> typically exhibit much lower mobility than in single layers [53]. Second, while a field effect gap as large as 200 meV has been verified optically, the corresponding transport gap is substantially reduced by disorder in electrical transport [54]. The use of hBN dielectrics as both top and bottom gate dielectrics may substantially overcome both of these issues [55]. Early experiments indicate that bilayer graphene fabricated on hBN dielectrics show superior transport characteristics in comparison to similarly fabricated monolayer devices [31]. Furthermore, encapsulated monolayer graphene devices with hBN forming both the top and bottom dielectrics (using the same fabrication techniques as outlined in Fig. 4) are found to show optimal transport in both the low-bias and high-bias regimes [35], [42], [56]. Provided that a similar hBN-encapsulated GFET structure would allow for comparable enhancements in the electronic properties of bilayer graphene (as have been observed for monolayer samples), a transport gap could be observable in bilayer GFETs, even at room temperature. So far, no studies have reported high-frequency characteristics of gapped monolayer or bilayer graphene devices.

This represents an important outstanding experiment that may enable a crucial step forward in graphene-based technologies, particularly when combined with further channel length scaling.

## V. WAFER-SCALE FABRICATION

A fundamental requirement for commercial electronic applications will be to develop wafer-scale processes for manufacturing both high-quality graphene and hBN. Growth of large-area films by chemical vapor deposition (CVD) grown on low-cost substrates promises a method to produce graphene suitable for commercial applications. Graphene growth has already made important advancements in the last few years [58], [59]. For example, it is now possible to grow single-crystalline graphene samples up to a few hundred micrometers in size [60], using optimized CVD growth techniques. By combining this largegrain growth with hBN dielectrics, it was recently shown that CVD-grown devices can exhibit transport quality comparable to those of graphene exfoliated from natural graphite [57], [61]. Fig. 12 shows the four-probe resistivity and field-effect mobility of such a sample with hBN dielectric. Remarkably, the field-effect mobility is close to 30 000 cm<sup>2</sup>/Vs at the highest density [57].

As the interest in hBN as a dielectric for graphene is rather new, limited large-scale growth capabilities for hBN films have been developed. However, there are recent attempts to grow controlled thickness of hBN [62]-[65], to directly grow graphene on hBN [66], and to grow

Fig. 12. CVD graphene on hBN [57]. (a) Upper panel shows an optical image of a large single-crystalline graphene flake grown by low-pressure CVD. Lower panel shows a Hall bar device fabricated after transferring the graphene to an hBN substrate. (b) Low-field transport measurements taken from the Hall-bar geometry shown in (a) (T = 1.5 Kelvin). Lower panel shows the field-effect mobility plotted as a function of carrier density. A high-density mobility of 30 000 cm<sup>2</sup>/Vs is measured, which is comparable to the best exfoliated devices on hBN, at equivalent carrier density.

alternating layers of graphene/hBN [67]. While these attempts are in their infancy and devices are currently of low quality, these techniques promise to soon enable fully scalable growth of graphene/hBN heterostructures for a wide range of applications [68].

## VI. CONCLUSION

In this review, we summarize the recent progress in using hBN as a dielectric for graphene FETs. The use of hBN significantly reduces impurities and charged traps associated with the gate dielectric and graphene/dielectric interface over metal-oxide alternatives. Additionally, fabrication of layered graphene/hBN heterostrucutres is accomplished without the need for an adhesion layer, allowing the intrinsic properties of the graphene channel to be maintained. I-V characteristics from hBN-supported

devices show saturating drain current behavior down to the shortest channel lengths currently measured (0.5  $\mu$ m) and to date yield the record peak dc voltage gain. RF measurements of these devices show significantly improved  $f_{\rm max}$  and, more importantly,  $f_{\rm max}/f_{\rm T}$  ratios. If continued channel-length scaling into the sub-100-nm region with saturating I-V characteristics can be achieved and device parasitics can be further controlled,  $f_{\text{max}}$  values approaching the terahertz regime may be expected. Further process development is necessary to realize wafer-scale growth of graphene/hBN heterostructures and enable fabrication of high-performance GFETs on a large scale. ■

# Acknowledgment

The authors would like to thank K. Watanabe and T. Taniguchi for supplying hBN crystals.

#### REFERENCES

- [1] A. K. Geim and K. S. Novoselov, "The rise of graphene," Nature Mater., vol. 6, no. 3, pp. 183-191, Mar. 2007.

- [2] A. K. Geim, "Graphene: Status and prospects," Science, vol. 324, no. 5934, pp. 1530-1534, Jun. 2009.

- [3] A. H. Castro Neto, F. Guinea, N. M. R. Peres, K. S. Novoselov, and A. K. Geim, "The electronic properties of graphene," Rev. Modern Phys., vol. 81, pp. 109-162,

- [4] F. Bonaccorso, Z. Sun, T. Hasan, and A. C. Ferrari, "Graphene photonics and optoelectronics," Nature Photon., vol. 4, pp. 611-622, Aug. 2010.

- [5] P. Avouris, "Graphene: Electronic and photonic properties and devices," Nano Lett., vol. 10, pp. 4285-4294, Nov. 2010.

- [6] K. Watanabe, T. Taniguchi, and H. Kanda, "Direct-bandgap properties and evidence for ultraviolet lasing of hexagonal boron nitride single crystal," *Nature Mater.*, vol. 3, no. 6, pp. 404-409, Jun. 2004.

- [7] G. Giovannetti, P. A. Khomyakov, G. Brocks, P. J. Kelly, and J. van den Brink, "Substrate-induced band gap in graphene on hexagonal boron nitride: Ab initio density functional calculations," Phys. Rev. B, vol. 76, no. 7, Aug. 2007, 73103.

- [8] R. Geick, C. H. Perry, and G. Rupprecht, "Normal modes in hexagonal boron nitride," Phys. Rev., vol. 146, no. 2, pp. 543-547, Jun. 1966.

- [9] N. Ohba, K. Miwa, N. Nagasako, and A. Fukumoto, "First-principles study on structural, dielectric, and dynamical properties for three BN polytypes, Phys. Rev. B, vol. 63, Mar. 2001, 115207.

- [10] A. Lipp and K. Schwetz, "Hexagonal boron nitride: Fabrication, properties and applications," J. Eur. Ceramic Soc., vol. 5, pp. 3-9, 1989.

- [11] S. I. Association, "The International Technology Roadmap for Semiconductors," Tech. Rep., 2009.

- [12] R. S. Shishir and D. K. Ferry, "Velocity saturation in intrinsic graphene," J. Phys., Condensed Matter, vol. 21, Aug. 2009, 344201.

- [13] S. Koswatta, A. Valdes-Garcia, M. Steiner, Y.-M. Lin, and P. Avouris, "Ultimate RF performance potential of carbon electronics," IEEE Trans. Microw. Theory Tech., vol. 59, no. 10, pp. 2739-2750, Oct. 2011.

- [14] J. Chauhan, L. Liu, Y. Lu, and J. Guo, 'A computational study of high-frequency behavior of graphene field-effect transistors," J. Appl. Phys., vol. 111, May 2012, 094313.

- [15] I. Meric, N. Baklitskaya, P. Kim, and K. Shepard, "RF performance of top-gated, zero-bandgap graphene fiel-effect transistors," in Proc. IEEE Int. Electron Devices Meeting, Nov. 2008, DOI: 10.1109/IEDM.2008. 4796738.

- [16] Y.-M. Lin, C. Dimitrakopoulos, K. A. Jenkins, D. B. Farmer, H.-Y. Chiu, A. Grill, and P. Avouris, "100-GHz transistors from wafer-scale epitaxial graphene," Science, vol. 327, no. 5966, p. 662, Feb. 2010.

- [17] D. B. Farmer, H.-Y. Chiu, Y.-M. Lin, K. A. Jenkins, F. Xia, and P. Avouris, "Utilization of a buffered dielectric to achieve high field-effect carrier mobility in graphene transistors," Nano Lett., vol. 9, no. 12, pp. 4474-4478, Dec. 2009.

- [18] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric,' Appl. Phys. Lett., vol. 94, Feb. 2009, 062107.

- [19] I. Meric, C. R. Dean, A. F. Young, N. Baklitskaya, N. J. Tremblay, C. Nuckolls, P. Kim, and K. L. Shepard, "Channel length scaling in graphene field-effect transistors studied with pulsed current-voltage measurements," Nano Lett., vol. 11, no. 3, pp. 1093-1097, Mar. 2011.

- [20] Y. Wu, Y.-M. Lin, A. A. Bol, K. A. Jenkins, F. Xia, D. B. Farmer, Y. Zhu, and P. Avouris, "High-frequency, scaled graphene transistors on diamond-like carbon," *Nature*, vol. 472, no. 7341, pp. 74-78, Apr. 2011.

- [21] I. Meric, M. Y. Han, A. F. Young, B. Ozvilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap top-gated graphene field-effect transistors," Nature Nanotechnol., vol. 3, no. 11, pp. 654-659, Nov. 2008.

- [22] A. Khakifirooz and D. Antoniadis, "Transistor performance scaling: The role of virtual source velocity and its mobility dependence," in Proc. IEEE Int. Electron Devices Meeting, 2006, DOI: 10.1109/IEDM.2006.346873.

- [23] R. Cheng, J. Bai, L. Liao, H. Zhou, Y. Chen, L. Liu, Y. Lin, S. Jiang, Y. Huang, and X. Duan, "High-frequency self-aligned graphene transistors with transferred gate stacks," Proc. Nat. Acad. Sci., vol. 109, no. 29, pp. 11 588-11 592, Jul. 2012.

- [24] J. Moon, D. Curtis, M. Hu, D. Wong, C. McGuire, P. Campbell, G. Jernigan, J. Tedesco, B. VanMil, R. Myers-Ward, C. Eddy, and D. Gaskill, "Epitaxial-graphene RF field-effect transistors on Si-Face 6H-SiC substrates," IEEE Electron Device Lett., vol. 30, no. 6, pp. 650-652, Jun. 2009.

- [25] Y. Wu, Y.-M. Lin, A. A. Bol, K. A. Jenkins, F. Xia, D. B. Farmer, Y. Zhu, and P. Avouris, "High-frequency, scaled graphene transistors on diamond-like carbon," Nature, vol. 472, no. 7341, pp. 74-78, Apr. 2011.

- [26] Y.-M. Lin, A. Valdes-Garcia, S. J. Han, D. B. Farmer, I. Meric, Y. Sun, Y. Wu, C. Dimitrakopoulos, A. Grill, P. Avouris, and K. A. Jenkins, "Wafer-scale graphene integrated circuit," *Science*, vol. 332, no. 6035, pp. 1294-1297, Jun. 2011.

- [27] Y. Wu, K. A. Jenkins, A. Valdes-Garcia, D. B. Farmer, Y. Zhu, A. A. Bol, C. Dimitrakopoulos, W. Zhu, F. Xia P. Avouris, and Y.-M. Lin, "State-of-the-art graphene high-frequency electronics, Nano Lett., vol. 12, no. 6, pp. 3062-3067, Jun. 2012.

- [28] K. Kim, J.-Y. Choi, T. Kim, S.-H. Cho, and H.-J. Chung, "A role for graphene in silicon-based semiconductor devices, Nature, vol. 479, no. 7373, pp. 338-344, Nov. 2011.

- [29] T. Taniguchi and K. Watanabe, "Synthesis of high-purity boron nitride single crystals under high pressure by using Ba BN solvent,"

- J. Crystal Growth, vol. 303, no. 2, pp. 525-529, May 2007.

- [30] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, "Electric field effect in atomically thin carbon films," Science, vol. 306, no. 5696, pp. 666-669, Oct. 2004.

- [31] C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard, and J. Hone, "Boron nitride substrates for high-quality graphene electronics," Nature Nanotechnol., vol. 5, no. 10, pp. 722-726, Oct. 2010.

- [32] S.-J. Han, K. A. Jenkins, A. Valdes-Garcia, A. D. Franklin, A. A. Bol, and W. Haensch, "High-frequency graphene voltage amplifier," Nano Lett., vol. 11, no. 9, pp. 3690–3693, Sep. 2011.

- [33] E. H. Hwang, S. Adam, and S. D. Sarma, "Carrier transport in two-dimensional graphene layers," Phys. Rev. Lett., vol. 98, no. 18, May 2007, 186806.

- [34] I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. Shepard, "Graphene field-effect transistors based on boron nitride gate dielectrics," in Proc. IEEE Int. Electron Devices Meeting, 2010, pp. 23.2.1-23.2.4.

- [35] A. S. Mayorov, R. V. Gorbachev, S. V. Morozov, L. Britnell, R. Jalil, L. A. Ponomarenko, P. Blake, K. S. Novoselov, K. Watanabe, T. Taniguchi, and A. K. Geim, "Micrometer-scale ballistic transport in encapsulated graphene at room temperature," Nano Lett., vol. 11, no. 6, pp. 2396-2399, Jun. 2011.

- [36] R. Decker, Y. Wang, V. W. Brar, W. Regan, H.-Z. Tsai, Q. Wu, W. Gannett, A. Zettl, and M. F. Crommie, "Local electronic properties of graphene on a BN substrate via scanning tunneling microscopy," *Nano Lett.*, vol. 11, no. 6, pp. 2291–2295, Jun. 2011.

- [37] J. Xue, J. Sanchez-Yamagishi, D. Bulmash, P. Jacquod, A. Deshpande, K. Watanabe, T. Taniguchi, P. Jarillo-Herrero, and B. J. LeRoy, "Scanning tunnelling microscopy and spectroscopy of ultra-flat graphene on hexagonal boron nitride," Nature Mater., vol. 10, no. 4, pp. 282-285, Apr. 2011.

- [38] J. Schiefele, F. Sols, and F. Guinea, "Temperature dependence of the conductivity of graphene on boron nitride," *Phys. Rev. B*, vol. 85, no. 1, May 2012, 195420.

- [39] C. R. Dean, A. F. Young, P. Cadden-Zimansky, L. Wang, H. Ren, K. Watanabe, T. Taniguchi, P. Kim, J. Hone, and K. L. Shepard, "Multicomponent fractional quantum Hall effect in graphene," Nature Phys., vol. 7, pp. 693-696, May 2011.

- [40] T. Taychatanapat, K. Watanabe, T. Taniguchi, and P. Jarillo-Herrero, "Quantum Hall effect and Landau-level crossing of Dirac fermions in trilayer graphene," Nature Phys., vol. 7, no. 8, pp. 621-625, Jun. 2011.

- [41] I. Meric, C. R. Dean, S.-J. Han, L. Wang, K. A. Jenkins, J. Hone, and K. L. Shepard, "High-frequency performance of graphene field effect transistors with saturating IV-characteristics," in Proc. IEEE Int. Electron Devices Meeting, 2011, DOI: 10.1109/IEDM. 2011.6131472.

- [42] H. Wang, T. Taychatanapat, A. Hsu, K. Watanabe, T. Taniguchi, P. Jarillo-Herrero, and T. Palacios, "BN/graphene/BN transistors for RF applications," IEEE Electron Device Lett., vol. 32, no. 9, pp. 1209-1211, Sep. 2011.

- [43] S.-J. Han, Y. Sun, A. Bol, W. Haensch, and Z. Chen, "Study of channel length scaling in large-scale graphene FETs," in Proc. Symp. Very Large Scale Integr. Technol., 2010, pp. 231–232.

- [44] Q. Liang, J. Cressler, G. Niu, Y. Lu, G. Freeman, D. Ahlgren, R. Malladi, K. Newton, and D. Harame, "A simple four-port parasitic deembedding methodology for high-frequency scattering parameter and noise characterization of SiGe HBTs," IEEE Trans. Microw. Theory Tech., vol. 51, no. 11, pp. 2165–2174, Nov. 2003.

- [45] F. Xia, V. Perebeinos, Y.-M. Lin, Y. Wu, and P. Avouris, "The origins and limits of metal-graphene junction resistance," *Nature Nanotechnol.*, vol. 6, no. 3, pp. 179–184, Mar. 2011.

- $\left[46\right]\,$  S. Das and J. Appenzeller, "On the importance of bandgap formation in graphene for analog device applications," IEEE Trans. Nanotechnol., vol. 10, no. 5, pp. 1093-1098, Sep. 2011.

- [47] M. Y. Han, B. Ozyilmaz, Y. Zhang, and P. Kim, "Energy band-gap engineering of graphene nanoribbons," Phys. Rev. Lett., vol. 98, no. 20, May 2007, 206805

- [48] X. Li, X. Wang, L. Zhang, S. Lee, and H. Dai, "Chemically derived, ultrasmooth graphene nanoribbon semiconductors, Science, vol. 319, no. 5867, pp. 1229-1232, Feb. 2008.

- [49] F. Schwierz, "Graphene transistors," Nature Nanotechnol., vol. 5, no. 7, pp. 487–496, Jul. 2010.

- [50] V. M. Pereira, A. H. Castro Neto, and N. M. R. Peres, "Tight-binding approach to uniaxial strain in graphene," Phys. Rev. B, vol. 80, no. 4, Jul. 2009, 45401.

- Y. Zhang, T.-T. Tang, C. Girit, Z. Hao, M. C. Martin, A. Zettl, M. F. Crommie, Y. R. Shen, and F. Wang, "Direct observation of a widely tunable bandgap in bilayer graphene," Nature, vol. 459, no. 7, pp. 820-823, Jun. 2009.

- [52] B. N. Szafranek, G. Fiori, D. Schall, D. Neumaier, and H. Kurz, "Current saturation and voltage gain in bilayer graphene field effect transistors," Nano Lett., vol. 12, no. 3, pp. 1324-1328, Mar. 2012.

- [53] S. Adam and S. Das Sarma, "Boltzmann transport and residual conductivity in bilayer graphene," *Phys. Rev. B*, vol. 77, no. 1, Mar. 2008, 115436.

- T. Taychatanapat and P. Jarillo-Herrero, "Electronic transport in dual-gated bilayer graphene at large displacement fields, Phys. Rev. Lett., vol. 105, no. 16, Oct. 2010, 166601

- [55] A. Ramasubramaniam, D. Naveh, and E. Towe, "Tunable band gaps in bilayer graphene-BN heterostructures," *Nano* Lett., vol. 11, no. 3, pp. 1070-1075, Mar. 2011.

- [56] L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov, and L. A. Ponomarenko, "Field-effect tunneling transistor based on vertical graphene heterostructures," Science, vol. 335, no. 6071, pp. 947-950, Feb. 2012.

- [57] N. Petrone, C. R. Dean, I. Meric, A. M. Van Der Zande, P. Y. Huang, L. Wang, D. Muller, K. L. Shepard, and J. Hone, "Chemical vapor deposition-derived

- graphene with electrical performance of exfoliated graphene," *Nano Lett.*, vol. 12, no. 6, pp. 2751–2756, Jun. 2012.

- [58] X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, and R. S. Ruoff, "Large-area synthesis of high-quality and uniform graphene films on copper foils," Science, vol. 324, no. 5932, pp. 1312-1314, Jun. 2009.

- [59] S. Bae, H. Kim, Y. Lee, X. Xu, J.-S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H. R. Kim, Y. I. Song, Y. J. Kim, K. S. Kim, B. Ozyilmaz, J.-H. Ahn, B. H. Hong, and S. Iijima, "Roll-to-roll production of 30-inch graphene films for transparent electrodes," Nature Nanotechnol., vol. 5, no. 8, pp. 574-578, Aug. 2010.

- [60] X. Li, C. W. Magnuson, A. Venugopal, R. M. Tromp, J. B. Hannon, E. M. Vogel, L. Colombo, and R. S. Ruoff, "Large-area graphene single crystals grown by low-pressure chemical vapor deposition of methane on copper," J. Amer. Chem. Soc., vol. 133, no. 9, pp. 2816-2819, Mar. 2011.

- [61] W. Gannett, W. Regan, K. Watanabe, T. Taniguchi, M. Crommie, and A. Zettl, "Boron nitride substrates for high mobility chemical vapor deposited graphene, Appl. Phys. Lett., vol. 98, no. 24, pp. 242105-1-242105-3, 2011.

- $[62]\,$  K. H. Lee, H.-J. Shin, J. Lee, I. Lee, G.-H. Kim, J.-Y. Choi, and S.-W. Kim, "Large-scale synthesis of high-quality hexagonal boron nitride nanosheets for large-area graphene electronics," Nano Lett., vol. 12, no. 2, pp. 714-718, Feb. 2012.

- [63] K. K. Kim, A. Hsu, X. Jia, S. M. Kim, Y. Shi, M. Hofmann, D. Nezich, J. F. Rodriguez-Nieva, M. Dresselhaus, T. Palacios, and J. Kong, "Synthesis of monolayer hexagonal boron nitride on cu foil using chemical vapor deposition,' Nano Lett., vol. 12, no. 1, pp. 161-166, Jan. 2012.

- [64] Y. Shi, C. Hamsen, X. Jia, K. K. Kim, A. Reina, M. Hofmann, A. L. Hsu, K. Zhang, H. Li, Z.-Y. Juang, M. S. Dresselhaus, L.-J. Li, and J. Kong, "Synthesis of few-layer hexagonal boron nitride thin film by chemical vapor deposition," Nano Lett., vol. 10, no. 10, pp. 4134-4139, Oct. 2010.

- [65] L. Song, L. Ci, H. Lu, P. B. Sorokin, C. Jin, J. Ni, A. G. Kvashnin, D. G. Kvashnin, J. Lou, B. I. Yakobson, and P. M. Ajayan, "Large scale growth and characterization of atomic hexagonal boron nitride layers," Nano Lett., vol. 10, no. 8, pp. 3209–3215, Aug. 2010.

- [66] M. Son, H. Lim, M. Hong, and H. C. Choi, "Direct growth of graphene pad on exfoliated hexagonal boron nitride surface," Nanoscale, vol. 3, no. 8, pp. 3089-3093, Aug. 2011.

- [67] Z. Liu, L. Song, S. Zhao, J. Huang, L. Ma, J. Zhang, J. Lou, and P. M. Ajayan, "Direct growth of graphene/hexagonal boron nitride stacked layers," *Nano Lett.*, vol. 11, pp. 2032-2037, May 2011.

- [68] M. S. Bresnehan, M. J. Hollander, M. Wetherington, M. Labella, K. A. Trumbull, R. Cavalero, D. W. Snyder, and J. A. Robinson, "Integration of hexagonal boron nitride with quasi-freestanding epitaxial graphene: Toward wafer-scale, high-performance devices," ACS Nano, vol. 6, no. 6, pp. 5234-5241, Jun. 2012.

### ABOUT THE AUTHORS

Inanc Meric received the B.S. degree in electrical engineering (with honors) from Bilkent University, Ankara, Turkey, in 2005 and the M.S. and Ph.D. degrees in electrical engineering from Columbia University, New York, NY, USA, in 2007 and 2011, respectively.

Since 2011, he has been a Postdoctoral Research Scientist at Columbia University in the Department of Electrical Engineering. His research interests include 2-D layered materials for novel

electronic applications such as graphene/hexagonal-boron-nitride fieldeffect transistors for radio-frequency (RF) and flexible electronics.

Cory R. Dean received the B.S. degree in mathematics (with distinction), the B.Sc. degree in physics (with honors), and the M.Sc. degree in physics from Queen's University, Kingston, ON, Canada, in 2000, 2001, and 2004, respectively, and the Ph.D. degree in physics from McGill University, Montreal, QC, Canada, in 2009.

From 2009 to 2013, he was a Postdoctoral Researcher at Columbia University, New York, NY, USA, in the Department of Electrical Engineering

and the Department of Mechanical Engineering and Physics. Currently, he is an Assistant Professor in the Department of Physics, The City College of New York, New York, NY, USA. His research interests include novel electron transport in mesoscale devices and emergent behavior in strongly interacting many-body quantum systems.

Dr. Dean was awarded an NSERC postdoctoral fellowship in 2009, as well as an NSERC doctoral fellowship in 2005. He was the recipient of the Carl Reindhardt Fellowship in 2008 and also in 2001, the R. Samuel McLaughlin Fellowship in 2003 and also in 2002, and the G. Neilson Whyite Graduate Fellowship in 2001. His Ph.D. dissertation was nominated for the Canadian National Dissertation Award by McGill University in 2009.

Nicholas Petrone received the B.S. degree in mechanical engineering from Johns Hopkins University, Baltimore, MD, USA, in 2005 and the M.S. degree in mechanical engineering from University of California Los Angeles, Los Angeles, CA, USA, in 2008. Currently, he is working toward the Ph.D. degree in the Department of Mechanical Engineering, Columbia University, New York, NY, USA.

His research interests include the synthesis of large-area films of graphene by chemical vapor

deposition as well as the fabrication and characterization of graphenebased flexible electronics, such as radio-frequency (RF) field-effect transistors (FETs) and transparent conductive electrodes.

Mr. Petrone is a member of Pi Tau Sigma, the American Society of Mechanical Engineers, the American Physical Society, and the Materials Research Society.

Lei Wang received the B.S. (first class honors) and M.S. degrees in electrical and computer engineering from National University of Singapore (NUS), Singapore, in 2005 and 2008, respectively. Currently, he is working toward the Ph.D. degree in electrical engineering at Columbia University, New York, NY, USA.

His research interests include electron transport in graphene, novel graphene/boron-nitride hereterostructures and graphene, boron-nitride, and molybdenum disulfide based electronic devices. James Hone received the B.S. degree in physics from Yale University, New Haven, CT, USA, in 1990 and the M.S. and Ph.D. degrees in physics from the University of California, Berkeley, Berkeley, CA, USA, in 1994 and 1998, respectively.

Currently, he is a Professor of Mechanical Engineering at Columbia University, New York, NY, USA. His research interests include carbon nanotubes, graphene, and other layered materials, and

Philip Kim received the B.S. degree in physics from Seoul National University, Seoul, Korea, in 1990 and the Ph.D. degree in applied physics from Harvard University, Cambridge, MA, USA, in 1999.

experimental condensed matter physics with an emphasis on physical properties and applications of nanoscale low-dimensional materials. Notably, in recent years, he has demonstrated novel transport phenomena in low-dimensional graphitic nanomaterials such as carbon nanotubes and graphene. He has published more than 100 papers.

Prof. Kim received numerous honors and awards, including the 2012 Dresden Barkhausen Award, the 2009 IBM Faculty Fellowship, and the 2008 Ho-Am Science Prize. He has been a Member of the American Physical Society Fellow since 2007.

Kenneth L. Shepard (Fellow, IEEE) received the B.S.E. degree from Princeton University, Princeton, NJ, USA, in 1987 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 1988 and 1992, respectively.

From 1992 to 1997, he was a Research Staff Member and Manager with the VLSI Design Department, IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, where he was respon-

sible for the design methodology for IBM's G4 S/390 microprocessors. Since 1997, he has been with Columbia University, New York, NY, USA, where he is now Professor of Electrical Engineering and Biomedical Engineering. He also was Chief Technology Officer of CadMOS Design Technology, San Jose, CA, USA, until its acquisition by Cadence Design Systems in 2001. His current research interests include power electronics, carbon-based devices and circuits, and complementary metal-oxidesemiconductor (CMOS) bioelectronics.

Dr. Shepard was Technical Program Chair and General Chair for the 2002 and 2003 International Conference on Computer Design, respectively. He has served on the Program Committees for International Electron Devices Meeting (IEDM), International Solid-State Circuits Conference (ISSCC), VLSI Symposium, International Conference on Computer-Aided Design (ICCAD), Design Automation Conference (DAC), International Symposium on Circuits and Systems (ISCAS), International Symposium on Quality Electronic Design (ISQED), Great Lakes Symposium on VLSI (GLS-VLSI), and International Conference on Computer Design (ICCD). He received the Fannie and John Hertz Foundation Doctoral Thesis Prize in 1992, a National Science Foundation CAREER Award in 1998, and the 1999 Distinguished Faculty Teaching Award from the Columbia Engineering School Alumni Association. He has been an Associate Editor of the IEEE TRANSACTIONS ON VERY LARGE-SCALE INTEGRATION (VLSI) SYSTEMS and is currently an Associate Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS and the IEEE Transactions on Biomedical Circuits and Systems.