# A unified charge-current compact model for ambipolar operation in quasi-ballistic graphene transistors: Experimental verification and circuit-analysis demonstration

Shaloo Rakheja<sup>1</sup>, Han Wang<sup>1</sup>, Tomás Palacios<sup>1</sup>, Inanc Meric<sup>2</sup>, Kenneth Shepard<sup>2</sup>, Dimitri Antoniadis<sup>1</sup>

<sup>1</sup>Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge MA 02139

<sup>2</sup> Department of Electrical Engineering, Columbia University, New York, NY 10027

## Abstract

This paper presents a compact virtual source (VS) model to describe carrier transport valid in both unipolar and ambipolar transport regimes in quasi-ballistic graphene fieldeffect transistors (GFETs). The model formulation allows for an easy extension to bi-layer graphene transistors, where a bandgap can be opened. The model also includes descriptions of intrinsic terminal charges/capacitances obtained selfconsistently with the transport formulation. The charge model extends from drift-diffusive transport regime to ballistic transport regime, where gradual-channel approximation (GCA) fails. The model is calibrated exhaustively against DC and S-parameter measurements of GFETs. To demonstrate the model capability for circuit-level simulations, the Verilog-A implementation of the model is used to simulate the dynamic response of frequency doubling circuits with GFETs operating in the ambipolar regime.

#### Introduction

With its rich physics, graphene has properties that make it a viable candidate for implementing a variety of highfrequency analog electronic devices such as frequency multipliers and mixers [1-2]. Because of its twodimensionality, graphene allows for a higher electrostatic integrity and holds the promise to scale to higher operating frequencies than Si or III-V counterparts. To design and simulate electronic devices made out of graphene, compact device models that include both transport description (static operation) as well as channel-charge information (dvnamic operation) are required. Most of the previous modeling efforts in GFETs have relied on the drift-diffusion (DD) theory of carrier transport with a density-dependent saturation velocity [3-5]. In this paper, an alternate transport model based on the concept of virtual source (VS) charge/velocity has been developed for GFETs; the model can describe negative differential resistance (NDR) in GFETs - a manifestation of ambipolar transport in the channel. The VS model for GFETs includes the degradation in mobility and VS carrier injection velocity due to carrier scatterings that are prevalent in quasi-ballistic transistors. A phenomenological model capturing the asymmetry in the contact resistance for electron and hole transports is also presented.

To describe the dynamic operation of the transistor, terminal charges as functions of various terminal voltages in the devices must be accounted for. The terminal charges are obtained self consistently with the transport formulation that can be extended all the way to the ballistic regime, where GCA is no longer valid. The resulting charges are smooth and have continuous derivatives enabling the model usage for complex circuit- and even system-level simulations as demonstrated through GFET-unique circuit simulation of frequency doublers.

### **Model description**

In the interest of brevity, only the essential model features are described – model details can be found online at [https://sites.google.com/site/shaloomit/home/equations-for-the-gfet-vs-model]. In the VS model [6], the FET current in saturation is given as the product of the areal charge density,  $Q_{x0}$ , at the virtual source and the carrier injection velocity,  $v_{x0}$ . Single-layer graphene, being a gapless material, has two virtual sources – one for electrons and another for holes – at opposite ends of the channel. The net current, therefore, is a superposition of the injected electron and hole currents and is given as

$$\begin{aligned} \frac{I_d}{W} &= (Q_{x0e} + Q_{x0h}) v_{xo} F_{sat} + \frac{I_{d,min}}{W}, \end{aligned} \tag{1} \\ I_{d,min} &= \mu \frac{W}{L_{\sigma}} Q_{min} V_{DS}', \end{aligned} \tag{2}$$

where W is the channel width,  $L_g$  is the channel length,  $Q_{x0e}$  and  $Q_{x0h}$  are the electron and hole concentrations at the respective VS point,  $Q_{min}$  is the background doping in the channel,  $\mu$  is the carrier mobility, and  $V_{DS}'$  is the intrinsic drain-source bias.  $F_{sat}$  is an empirical function to achieve transition from the linear to saturation regimes of transport.  $F_{sat}$  is given as

$$F_{sat} = \frac{V_{DS}^{\prime}/V_{DSAT}}{\left(1 + \left(\frac{V_{DS}^{\prime}}{V_{DSAT}}\right)^{\beta}\right)^{\frac{1}{\beta}}},$$

(3)

$$V_{DSAT} = \frac{v_{x0}L_g}{\mu}.$$

(4)

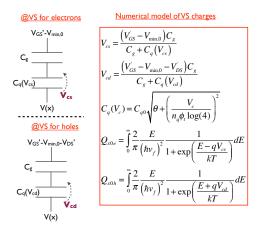

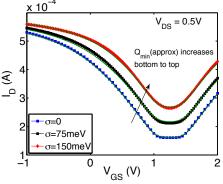

The carrier densities  $Q_{x0e}$  (electron VS) and  $Q_{x0h}$  (hole VS) can be determined numerically using the Fermi-Dirac integral and density-of-states (DOS) broadening, where the surface potentials at the source and drain ends are computed using a capacitance voltage divider as shown in Fig. 1. Alternatively,  $Q_{x0e}$  and  $Q_{x0h}$  can be computed using compact expressions [6] typically valid in materials with a bandgap. Remarkable agreement in computed current is obtained using the two approaches by adjusting background charge concentration (due to DOS broadening around the Dirac point) and gate capacitance (to account for finite quantum capacitance in graphene) as shown in Fig. 2; for purposes of this paper, we proceed with the compact  $Q_{x0e}$  and  $Q_{x0h}$  expressions, which reduce computation time and allow extension of the model to bi-layer graphene where a bandgap can be opened.

Fig. 1: (lhs) Voltage-divider network at the VS for electrons and holes.  $V_c$  denotes the surface potential, while  $C_q$  is the  $V_c$ -dependent quantum capacitance. The parameters  $\theta$  and  $n_q$  depend upon the density-of-states (DOS) broadening. For no DOS broadening,  $\theta=1 \& n_q=1$  [5]. (rhs) Numerical computation of VS charge concentration.

Fig. 2: Comparison of transfer characteristics obtained from the methodology in Fig. 1 and upon using compact model for VS charges. Here,  $\sigma$  denotes the DOS broadening. The compact model gives an excellent match by only adjusting background charge and gate capacitance.

The mobility of the carriers is adjusted to account for selfheating [7]. Further, mobility and VS injection velocity are appropriately reduced due to density-dependent carrier scatterings that are prevalent in quasi-ballistic GFETs [7-8].

$$\mu(T) = \frac{\mu_{0}}{\left(1 + \left(\frac{R_{th}I_{D}V_{DS}'}{T_{ref}}\right)^{\beta_{\mu}}\right)\left(1 + \left(\frac{Q_{x0e} + Q_{x0h}}{q_{e}n_{ref,\mu}}\right)^{\alpha_{\mu}}\right)}, \quad (5)$$

$$v_{x0} = \frac{v_{x00}}{\left(1 + \left(\frac{Q_{x0e} + Q_{x0h}}{q_{e}n_{ref,v}}\right)^{\alpha_{\nu}}\right)}. \quad (6)$$

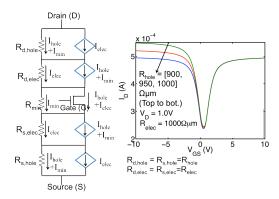

where  $R_{th}$  is the thermal resistance,  $\beta_{\mu}$ ,  $\alpha_{\mu}$ ,  $n_{ef,\mu}$ ,  $\alpha_{v}$ ,  $n_{ref,v}$  are fitting parameters taken from [7-8]. Asymmetry in the electron and hole branches of current conduction is introduced through asymmetric channel access resistances for electron and current branches as shown in Fig. 3, since theoretically the mobility and injection velocity of electrons and holes in graphene must be identical. Fig. 4 shows the transfer characteristics of a GFET with asymmetry.

The intrinsic terminal charges associated with source, drain, and gate terminals are determined self-consistently with the transport model as in [9]. Assuming a linear potential profile

Fig. 3: (lhs) A phenomenological equivalent circuit model to capture asymmetry in the contact resistances corresponding to electron and hole transports. (rhs) Transfer characteristics of a GFET with varying  $R_{hole}$  shows how the transfer curves become asymmetric.

along the channel and by enforcing current continuity and energy conservation, while allowing for a fraction, 1- $\zeta$ , of energy loss in quasi-ballistic ( $\zeta < I$ ) conditions, the voltagedependent terminal charges in the ballistic regime are obtained using (7)-(12) The two important parameters for ballistic charges are the effective carrier mass (m\*)[10] and  $\zeta$ .

$$\mathbf{v}_{\mathbf{x}}(\mathbf{x}) = \mathbf{v}_{\mathbf{x}0} \sqrt{1 + \mathbf{k} \frac{x}{L_g}} \tag{7}$$

$$k = \frac{2q_e \zeta V'_{DS}}{m^* v_{xo}^2} \tag{8}$$

$$Q_{SB} = (-Q_{x0e}F_1 + Q_{x0h}F_2)WL_g$$

(9)

$$Q_{DB} = (-Q_{x0e}F_2 + Q_{x0h}F_1)WL_g$$

(10)

$$F_1 = \frac{2}{3k^2} \left[ (2k+2)\sqrt{k+1} - (2+3k) \right] \quad (11)$$

$$F_2 = \frac{2}{3k^2} [(k-2)\sqrt{k+1} + 2]$$

(12)

At low drain-source bias ( $V_{DS}$ ), the devices are operating nearly in the DD non-velocity saturated (NVSAT) regime. The NVSAT charges are obtained assuming validity of GCA throughout the channel as in [11]. Transition between the two regions is accomplished using the same  $F_{sat}$  function. Outerfringing capacitances are also included in the model. The model has been implemented in MATLAB and Verilog-A.

#### **Comparison to experimental data**

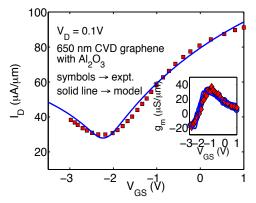

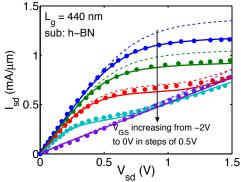

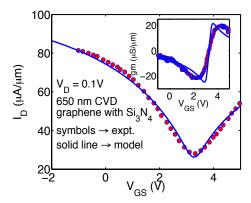

The GFET VS model is verified with experimental results, and extracted parameters are shown in Table I. Figs. 5 and 6 show the transfer characteristics and  $g_m (=\partial I_D / \partial V_{GS})$  of 650 nm CVD GFET devices on diamond-like carbon (DLC) substrate with Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub> dielectric from IBM [12]. Fig. 7 shows the experimental data from 440 nm exfoliated GFET on h-BN [13]. In these devices, the thermal resistance is very low, and Joule heating is negligible despite the high currents [13]. However, degradation in injection velocity resulting from carrier scattering is important at high bias as shown by the dashed lines in Fig. 7.

Fig. 5: Transfer curve at  $V_{os}$ =0.1 V for a 650 nm CVD GFET on DLC substrate with Al<sub>2</sub>O<sub>3</sub> gate dielectric [12]. Inset shows  $g_*$  versus  $V_{os}$  at a  $V_{os}$  of 0.1V.

Fig. 7: Output curves at various  $V_{\omega}$  for a 440 nm exfoliated GFET on hexagonal boron nitride (h-BN) substrates [13]. Model fits are shown in solid lines, while symbols are for the experimental data. Dashed lines are produced using the model but without considering the degradation in injection velocity due to carrier-scattering effects.

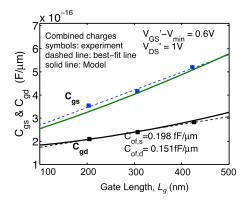

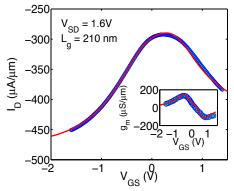

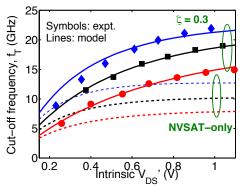

Figs. 8-10 correspond to CVD GFET devices on sapphire substrate with Al<sub>2</sub>O<sub>3</sub> dielectric in [14] with  $L_g = 210$  nm, 311 nm, and 430 nm. At the current densities observed experimentally and with the relatively high thermal conductance of sapphire, Joule heating is expected to be minimal. The gate capacitances obtained from the compact model with m\*=0.06m<sub>0</sub> &  $\zeta$ =0.3 result in good match with those obtained experimentally for these devices (Fig. 9); the cut-off frequency,  $f_T$ , is plotted in Fig. 10 for various L<sub>g</sub>. It can be seen that the pure DD-NVSAT model underestimates  $f_T$  for these devices because it overestimates charges and capacitances, particularly at high V<sub>DS</sub>.

Fig. 6: Fig. 6: Transfer curve at  $V_{as}$ =0.1 V for a 650 nm CVD GFET on DLC substrate with Si<sub>3</sub>N<sub>4</sub> gate dielectric [12]. Inset shows  $g_*$  versus  $V_{as}$  at a  $V_{as}$  of 0.1 V.

Fig. 8: Transfer curve for 210 nm CVD graphene device on sapphire substrate and Al<sub>2</sub>O<sub>3</sub> dielectric for  $V_{su}$ =1.6 V from [14]. The inset shows  $g_{*}$  as a function of  $V_{cs}$ . Model fits are shown in solid lines, while experimental data is shown in circles.

Fig. 9:  $C_{gs}$  and  $C_{gd}$  versus  $L_g$ . Measured data from [14]. Also shown is the best-fit line (dashed) from the measured data.

Figure 10: Simulated and measured  $f_T$  for devices in [14] for L<sub>g</sub>=210 nm (triangles), 311 nm (squares), 430 nm (circles). Dashed lines consider NVSAT-only charges, while solid lines represent the QB model with m<sup>\*</sup>=0.06m<sub>0</sub> and  $\zeta$ =0.3.

#### **GFET-unique circuit simulation**

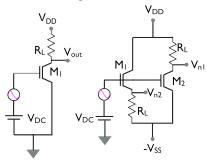

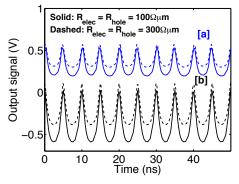

Fig. 11 shows two topologies of frequency-doubler circuits. The proposed new differential-output topology is expected to have significantly better performance than the previously demonstrated single-ended doubler [15] due to circuit symmetry. Fig. 12 shows the time-domain response of both

circuit topologies; the output voltage for both topologies can be increased with lower channel access resistances. In the differential-output topology, the feed-forward of the fundamental component is pushed to a much higher frequency as shown in Fig. 13.

Fig. 11: (lhs) A single-ended GFET frequency doubler. (rhs) A differentialoutput GFET frequency doubler.  $R_L$  is the load resistance, and the gate bias  $V_{DC}$  is the Dirac point voltage for both circuits. The output in the differential circuit is taken as  $V_{n1}$ - $V_{n2}$ .

Fig. 12: Time-domain response of single- [a] and differential-output [b] frequency-doubler circuits. The input signal is sinusoidal 2 V peak-to-peak with a frequency of 100 MHz.  $V_{DD}=1$  V for [a], and  $V_{DD}=V_{SS}=0.5$  V for [b].  $R_L = 2 \text{ K}\Omega$ . Other parameters are for the 210 nm device.

#### Conclusions

A physics-based compact model to describe ambipolar transport in graphene FETs has been developed. The model has been extensively verified against fabricated devices with a wide range of channel lengths and combination of substrate/dielectric environments. The model is also demonstrated in GFET-unique circuit analysis showing its potential for circuit and even system-level applications.

Fig. 13: Comparison of single- and differential-ended frequency doubler circuits (Fig. 12). The symbol [c] stands for the single-ended topology, while [d] stands for differential-ended topology.  $V_{DD}=1$  V for [c] and  $V_{DD}=V_{SS}=$ 0.5V for [d]. Device parameters same as for Fig. 12.

#### Acknowledgement:

Shaloo Rakheja and Dimitri Antoniadis acknowledge the support of NSF through the NCN-NEEDS program under contract 1227020-EEC and MIT SMART/LEES program. Han Wang and Tomás Palacios acknowledge the partial funding support provided by the Army Research Laboratory and the ONR GATE MURI program. Inanc Meric and Kenneth Shepard acknowledge the support of DARPA under contract ONR-N000141210014 and the AFOSR under contract FA9550-09-1-0705.

#### **References:**

[1] A.H. Castro Neto et al., Rev. of Mod. Phys., vol. 81, no. 1, pp. 109-162, 2009.

[2] H. Wang et al., IEEE Elec. Dev. Lett., vol. 31, no. 9, p. 906, 2010.

[3] I. Meric et al., Nature Nanotechnology, vol. 3, p. 654, Nov. 2008.

[4] W. Zhu et al., The Intl' Conf. on Simulation of Semiconductor Processes and Devices (SISPAD), 5-7 Dec., Colorado, 2012.

[5] K.N. Parrish et al., The Int'l Conf. on Simulation of Semiconductor Processes and Devices (SISPAD), 5-7 Dec., Colorado, 2012.

[6] A. Khakifirooz et al., IEEE Trans. on Elec. Dev., vol. 56, no. 8, p. 1674, Aug. 2009.

[7] V.E. Dorgan et al., App. Phys. Lett. 97, p. 082112, 2010.

[8] M.-H. Bae et al., ACS NANO, vol. 5, no. 10, p. 7936, 2011.

[9] L. Wei et al., IEEE Trans. on Elec. Dev., vol. 59, no. 5, p. 1263 May 2012.

[10] K.S. Novoselov et al., Nature 438, pp. 197-200, Sep. 2005.

[11] D. Jimenez, IEEE Trans. on Elec. Dev., vol. 58, no. 12, p. 4377, Dec. 2011.

[12] Y. Wu et al., Nano Letters, vol. 12, p. 3062, 2012.

[13] I. Meric et al., IEEE Int'l Elec. Dev. Meeting (IEDM), 6-8 Dec, 2010.

[14] H. Wang et al., IEEE Elec. Dev. Lett., vol. 33, no. 3, p. 324, Mar. 2012.

[15] H. Wang et al., IEEE Int'l Elec. Dev. Meeting (IEDM), 6-8 Dec., 2010.

| Table I: Parameter values for the VS GFET model                                                          |                                          |                                          |                      |                      |

|----------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|----------------------|----------------------|

| Parameter                                                                                                | 650 nm (Al <sub>2</sub> O <sub>3</sub> ) | 650 nm (Si <sub>3</sub> N <sub>4</sub> ) | 440 nm (h-BN)        | 210 nm               |

| Gate capacitance, $C_g (\mu F/cm^2)$                                                                     | 0.38                                     | 0.38                                     | 0.363                | 0.35                 |

| Dirac Voltage, $V_{min,0}$ (V)                                                                           | -2.25                                    | 3.22                                     | 0.105                | 0.95                 |

| Electron-branch resistance, $R_{elec}$ ( $\Omega\mu m$ )                                                 | 260                                      | 520                                      | 320                  | 1820                 |

| Hole-branch resistance, $R_{hole} (\Omega \mu m)$                                                        | 560                                      | 400                                      | 210                  | 1580                 |

| Low-field Mobility, $\mu_0$ (cm <sup>2</sup> /Vs)                                                        | 1000                                     | 900                                      | 6000                 | 1666                 |

| Virtual-source injection velocity, $v_{x00}$ (cm/s)                                                      | $2.0 \times 10^{7}$                      | $2.0 \times 10^{7}$                      | $2.1 \times 10^{7}$  | $1.4 \times 10^{7}$  |

| Minimum background charge, $Q_{min}$ (C/cm <sup>2</sup> )                                                | 1.85×10 <sup>-7</sup>                    | 1.75×10 <sup>-7</sup>                    | 1 ×10 <sup>-9</sup>  | $1.1 \times 10^{-8}$ |

| Lateral field saturation factor, $\beta$                                                                 | 2.0                                      | 2.0                                      | 1.65                 | 1.2                  |

| Carrier scattering parameter for velocity, $n_{ref,v}$ (cm <sup>-2</sup> )                               |                                          |                                          | $1.1 \times 10^{14}$ | $1.1 \times 10^{14}$ |

| Parameters taken from References [7] & [8] for mobility and injection velocity degradation in Eq. 5 & 6: |                                          |                                          |                      |                      |

| Self-heating parameter for mobility, $\beta_{\mu}$ [7]                                                   |                                          |                                          | 3.0                  | 3.0                  |

| Carrier scattering parameter for mobility, $\alpha_{\mu}$ [7]                                            |                                          |                                          | 2.2                  | 2.2                  |

| Carrier scattering parameter for mobility, $n_{ref,\mu}$ (cm <sup>-2</sup> ) [7]                         |                                          |                                          | $1.1 \times 10^{13}$ | $1.1 \times 10^{13}$ |

| Carrier scattering parameter for velocity, $\alpha_v$ [8]                                                |                                          |                                          | 0.5                  | 0.5                  |