# 1200 V GaN Vertical Fin Power Field-Effect Transistors

Y. Zhang<sup>1\*</sup>, M. Sun<sup>1\*</sup>, D. Piedra<sup>1</sup>, J. Hu<sup>1</sup>, Z. Liu<sup>2</sup>, Y. Lin<sup>1</sup>, X. Gao<sup>3</sup>, K. Shepard<sup>4</sup>, and T. Palacios<sup>1</sup>

<sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA, USA, email: {yhzhang, minsun, tpalacios}@mit.edu

<sup>2</sup>Singapore-MIT Alliance for Research and Technology, Singapore

<sup>3</sup>IQE RF LLC, Somerset, NJ, USA

<sup>4</sup>Columbia University, New York, USA

\*These two authors contributed equally to this work.

Abstract—We demonstrate record performance in a novel normally-off GaN vertical transistor with submicron finshaped channels. This vertical fin transistor only needs n-GaN layers, with no requirement for epitaxial regrowth or p-GaN layers. A specific on-resistance of 0.2 mΩ·cm² and a breakdown voltage over 1200 V have been demonstrated with extremely high ON current (over 25 kA/cm²) and low OFF current at 1200 V (below 10<sup>-4</sup> A/cm²), rendering an excellent Baliga's figure of merit up to 7.2 GW/cm². A threshold voltage of 1 V was achieved and was stable up to 150 °C. Large devices with high current up to 10 A and breakdown voltage over 800 V were also demonstrated. These results show the great potential of GaN vertical fin transistors for high-current and high-voltage power applications.

#### I. Introduction

Lateral and vertical GaN-based devices are excellent candidates for high-power electronics. Vertical GaN devices have several potential advantages over lateral devices: 1) higher breakdown voltage (*BV*) and current for a given chip area; 2) superior reliability and 3) easier thermal management [1]. Until now, two main structures have been demonstrated for vertical GaN power transistors: current-aperture vertical electron transistor (CAVET) [2-4] and trench MOSFET [5-6].

Despite the blocking capability over 1200 V demonstrated in GaN transistors, the development of vertical GaN power transistors has been hindered by the requirement for epitaxial regrowth or p-type GaN. The epitaxial regrowth (e.g. required for CAVETs) greatly increases the complexity and cost of device fabrication. P-type GaN (e.g. required for fabricating trench MOSFETs) has low ratio for the acceptor activation as well as much lower carrier mobility compared to that in n-GaN. It is also difficult to make normally-off CAVETs due to the polarization in AlGaN/GaN heterojuncitons. To overcome these challenges, our group recently demonstrated a novel device structure, the GaN vertical fin power field-effect transistor (FET) [6]. This transistor only needs n-GaN layers with no requirement for p-GaN or epitaxial regrowth. A BV of 800 V, an on-resistance ( $R_{\rm on}$ ) of 0.36 m $\Omega$ ·cm<sup>2</sup> and normallyoff operation have been demonstrated [6]. However, higher BV and current are needed to justify the competitiveness of this novel device for high power applications.

In this work, by improving wafer structure, electric field (E-field) engineering and Ohmic contact techniques, we

successfully demonstrated a BV of 1200 V with an  $R_{on}$  of 0.2 m $\Omega$ ·cm<sup>2</sup> in normally-off GaN vertical fin power FETs. Large devices with a current of 10 A were also demonstrated.

# II. DEVICE DESIGN & FABRICATION

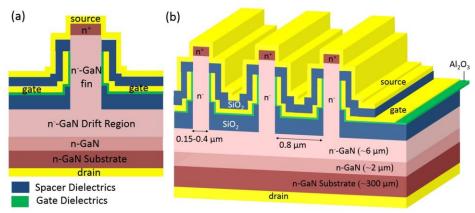

In vertical fin power FETs (**Fig. 1**), the current is controlled through fin-shaped vertical n-GaN channels, which are surrounded by gate dielectrics and metal electrodes. At zero gate bias, the electrons in the fin channels are depleted due to the work function difference between the gate metal and GaN. By shrinking the fin width below 500 nm, the depletion regions induced by the two free surfaces of the fin merge, fully depleting the fin channel and inducing a normally-off transistor operation. At increased gate bias, the depletion width decreases and electrons accumulate at the dielectric-GaN interfaces, forming conduction channels.

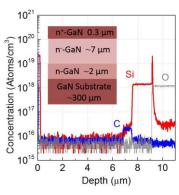

The epitaxial structure consists of 0.3  $\mu$ m-thick n<sup>+</sup>-GaN cap layer, 7  $\mu$ m-thick n<sup>-</sup>-GaN drift layer and 2  $\mu$ m-thick n-GaN layer, grown by MOCVD on free-standing GaN substrates (**Fig. 2**). The drift region was doped with carbon to compensate the non-intentional-doping in GaN (**Fig. 2**). A net donor concentration of ~3×10<sup>15</sup> cm<sup>-3</sup> was measured in the drift region, from the *C-V* measurement of vertical Schottky barrier diodes fabricated after removing the n<sup>+</sup>-GaN cap layer (**Fig. 3**).

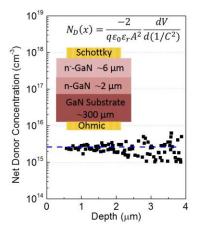

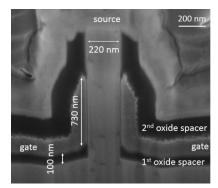

The device fabrication (Fig. 4) starts with the formation of the sub-micron fins aligned to a-plane by optimized Cl<sub>2</sub>/BCl<sub>3</sub>based dry etching following a hot TMAH treatment for corner rounding [8]. A first oxide spacer was then deposited by PECVD and etched down to near the bottom fin corner. The oxide etching depth was controlled by a timed photoresist (PR) etch (Fig. 4(a)). An Al<sub>2</sub>O<sub>3</sub> gate dielectric layer was then deposited by ALD followed by a sputtered Molybdenum gate layer. Then the gate metal and dielectrics were etched by the PR-assisted etching technique. A second oxide spacer was then deposited following a PR-assisted etch to expose top GaN surface. Before Ohmic metal deposition, a shallow cap layer recess was used to remove the highly-resistive layer induced by the plasma damage in previous steps and roughen the top GaN surface (Fig. 4(c)). This recess etch is key to make Ohmic contact to submicron-fins (Fig. 4(d)). Finally, Ti/Al metal stack was sputtered on the top/back side of the wafer for source/drain electrodes, with no need for post annealing. Fig. 5 shows the cross-section scanning electron microscopy image of the fin region in the fabricated transistor.

#### III. EXPERIMENTAL RESULTS

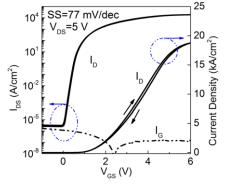

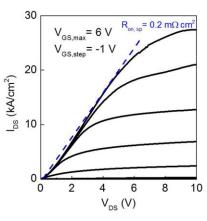

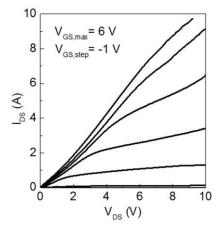

**Fig. 6** shows the transfer characteristics of a GaN vertical fin FET consisting of 60 fins with 200 nm fin width and 100 μm fin length. The extracted threshold voltage ( $V_{th}$ ) is ~1 V with almost no hysteresis. The  $I_{on}/I_{off}$  ratio is ~10<sup>10</sup> with extremely low gate leakage current. **Fig. 7** shows the device output characteristics. A  $R_{on}$  of 0.2 mΩ·cm² was extracted normalized to the total active fin area. If normalized to the total device area, the  $R_{on}$  is ~1 mΩ·cm² and can be further reduced by shrinking the lateral distance between fins.

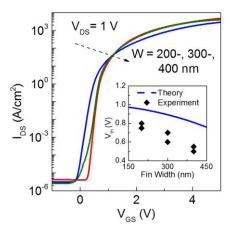

**Fig. 8** plots the transfer curves and  $V_{th}$  of transistors with different fin width (W). A smaller W provides better gate control and smaller subthreshold swing. The  $V_{th}$  of our vertical fin transistor can be analytically estimated by [9]:

$$V_{th} \approx V_{bi} - qQ_{ox}/\epsilon_{ox} - qN_DW^2/8\epsilon_{GaN} \tag{1}$$

The experimental  $V_{th}$  is lower than the  $V_{th}$  calculated by considering the barrier height  $(V_{bi})$  and W. This indicates the existence of positive charges at  $Al_2O_3/GaN$  interfaces  $(Q_{ox})$ . This charge was also reported in GaN lateral transistors [10].

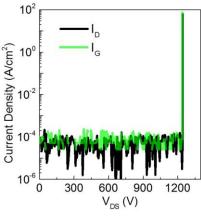

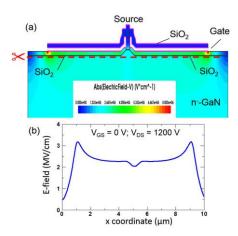

Fig. 9 shows the representative off-state characteristics of a GaN vertical fin FET consisting of 60 fins. A BV over 1200 V was demonstrated with extremely low drain and gate leakage current (<1 nA, close to measurement limit) at high drain bias. The breakdown was destructive and occured at the gate edge. This breakdown behavior can be well explained by the simulated E-field distribution at 1200 V (Fig. 10). As shown, the peak E-field happens at the gate edges instead of the bottom of the fins thanks to two key field engineering structures: (a) tapered-fin-bottom [8] with rounded corners, and (b) the oxide spacer layer between the gate electrode and fin corner, which forms a field-plate structure. Compared to the peak E-field at the fin corners, the peak E-field at the gate edge would be much easier to manage and can be further suppressed by adding additional gate and source field plates.

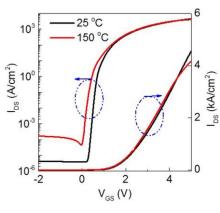

**Fig. 11** shows the representative device transfer characteristics at 150 °C and 25 °C, respectively. As shown, a small  $V_{\rm th}$  decrease (<0.15 V) was observed, demonstrating good thermal stability for normally-off operation.

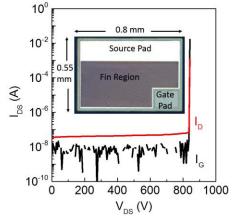

**Fig. 12** and **13** shows the demonstration of large-area GaN vertical fin power transistors with current rating of 10 A. The transistor consists of over 600 fins with a fin width of 250 nm in each fin. The total device size is  $0.8 \text{ mm} \times 0.55 \text{ mm}$ , which is significantly smaller than other 10 A-class GaN vertical and lateral transistors [5][11]. The gate drive for 10 A current is  $5\sim6$  V, which is smaller than that in vertical trench MOSFET ( $\sim10$  V [5]). A *BV* over 800 V was demonstrated in these large-size GaN vertical fin power transistors.

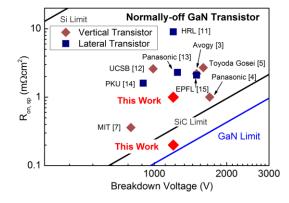

**Fig. 14** benchmarks the  $R_{\rm on}$  *v.s.* BV for our GaN vertical fin power FETs with other normally-off lateral and vertical GaN transistors. With a BV of 1200 V and  $R_{\rm on}$  of 0.2 mΩ·cm² (normalized to total fin area) or 1.0 mΩ·cm² (normalized to total device area), our device demonstrated a Baliga's figure of merit up to 7.2 GW/cm² (1.44 GW/cm² if normalized to total device area), which is among the best in all reported

normally-off GaN transistors. The  $R_{\rm on}$  of our vertical fin power FETs normalized to total device area can be further reduced by reducing the lateral distance between fins and increasing the fin aspect ratio, while the BV can be further improved by incorporating multiple gate and source field plates to smoothen the peak E-field at the gate edge.

**Table I** summarizes the key device metrics of our vertical fin power FETs, including  $R_{\rm on}$ , BV,  $V_{\rm th}$ , on-state drain-to-source saturation current density ( $I_{\rm ON,\ SAT}$ ), off-state leakage current density ( $I_{\rm OFF}$ ) at 1200 V and large device performance, benchmarked with other reported normally-off lateral and vertical transistors with high-current ratings. As shown, our vertical fin power FETs show the highest current density and the second lowest  $I_{\rm OFF}$  at 1200 V. Considering the significant reduction in epitaxy cost and complexity compared to other vertical GaN transistors, our GaN vertical fin power FETs are highly competitive for 1200-V level high power applications.

# IV. CONCLUSION

This work demonstrates a novel GaN vertical fin power FETs with a BV over 1200 V and a  $R_{\rm on}$  of  $0.2~{\rm m}\Omega\cdot{\rm cm}^2$ , as well as extremely high ON current density and low OFF current. This device can achieve normally-off operation, with a stable  $V_{\rm th}$  up to 150 °C. In addition, this device can greatly reduce the epitaxy cost and complexity compared to other GaN vertical power transistors. This performance demonstrates the great potential of GaN vertical fin FETs for high-power applications.

# ACKNOWLEDGMENT

This work was supported by the ARPA-E SWITCHES program monitored by Dr. T. Heidel and Dr. I. Kizilyalli.

# REFERENCES

- Y. Zhang et al., IEEE Transactions on Electron Devices, vol. 60, no. 7, pp. 2224–2230, Jul. 2013.

- [2] R. Yeluri et al., Applied Physics Letters, vol. 106, no. 18, p. 183502, May 2015.

- [3] H. Nie et al., IEEE Electron Device Letters, vol. 35, no. 9, pp. 939–941, Sep. 2014.

- [4] D. Shibata et al., in 2016 IEEE International Electron Devices Meeting (IEDM), 2016, p. 10.1.1-10.1.4.

- [5] T. Oka et al., in 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 459–462.

- [6] T. Oka et al., Appl. Phys. Express, vol. 7, no. 2, p. 021002, Jan. 2014.

- [7] M. Sun et al., IEEE Electron Device Letters, vol. 38, no. 4, pp. 509– 512, Apr. 2017.

- [8] Y. Zhang et al., Appl. Phys. Lett., vol. 110, no. 19, p. 193506, May 2017.

- [9] M. Sun, Ph. D. dissertation, Dept. Elec. Eng., Massachusetts Institute of Technology, Cambridge, MA, 2017.

- [10] Y. Zhang et al., Applied Physics Letters, vol. 103, no. 3, p. 033524, Jul. 2013.

- [11] R. Chu et al., IEEE Electron Device Letters, vol. 32, no. 5, pp. 632–634, May 2011.

- [12] C. Gupta et al., IEEE Electron Device Letters, vol. 38, no. 3, pp. 353–355, Mar. 2017.

- [13] M. Ishida et al., IEEE Transactions on Electron Devices, vol. 60, no. 10, pp. 3053–3059, Oct. 2013.

- [14] M. Wang et al., IEEE Transactions on Electron Devices, vol. 61, no. 6, pp. 2035–2040, Jun. 2014.

- [15] J. Ma et al., IEEE Electron Device Letters, vol. 38, no. 3, pp. 367–370, Mar. 2017.

Fig. 1. (a) Cross-sectional schematic of a device fin unit-cell and (b) side-view three-dimensional schematic of the proposed vertical GaN fin power field-effect transistors (FETs) with multiple fins. The fin length is  $\sim 1 \mu m$  in the vertical direction.

Fig. 2. GaN-on-GaN wafer epi-structure used in this work, and the Si, C and O ion profiles in the top layers of the wafer structure revealed by Secondary-ion mass spectrometry measurements.

Fig. 3. Net donor concentration as a function of depth in n<sup>-</sup>-GaN drift region, revealed by C-V measurement. (Inset I) Vertical Schottky barrier diodes fabricated for the C-V measurement. The top ~1  $\mu$ m GaN layer was etched before the diode fabrication. (Inset II) Formula used for the donor concentration derivation from C-V measurement.

Fig. 4. (a) Illustrative process for the formation of first  $SiO_2$  spacer in the fin structure, enabled by the timed etch and thickness control of the photoresist (PR) layer. (b) Key process steps to fabricate GaN vertical fin power FETs. (c) Scanning electron microscopy (SEM) images of the fins after the cap layer recess and surface roughening. (d) *I-V* characteristics of two Ohmic test structures, one with cap layer recess and the other without. The front and back sides of the Ohmic test structures are both covered by Ti/Al. The test device area is  $100\times25~\mu\text{m}^2$ . No post-deposition annealing was implemented for either structures.

Fig. 5. SEM cross section view of the fin area in a fabricated GaN vertical fin power FET with ~220 nm channel width.

Fig. 6. Double-sweep transfer curves of the fabricated vertical fin power FET with 200 nm channel width, with the  $V_{\rm DS}$  at 5 V. The left y-axis is in log scale with the right y-axis in linear scale. A threshold voltage of ~ 1 V can be extracted from linear extrapolation or defined at  $I_{\rm on}/I_{\rm off}$ =10<sup>5</sup>.

Fig. 7. Output characteristics of the fabricated fin power FET with channel width of 200 nm.

Fig. 8. Transfer curves of the fabricated GaN vertical fin power FETs with the fin widths of 200, 300 and 400 nm. (Inset) Threshold voltage  $(V_{th})$  as a function of fin width from experiment and analytical calculation. The  $V_{

m th}$  was extracted at a current level of 1 A/cm<sup>2</sup>.

Fig. 9. Off-state I-V characteristics for drain and gate leakage in the fabricated GaN vertical fin power FET, at a  $V_{GS}$  of 0 V. The breakdown is destructive in the oxide spacer layer at the gate edge. The leakage current is noisy as it is close to the measurement limit.

Fig. 10. (a) Simulated E-field distribution in the fin region when the vertical fin FET is biased at 1200 V in the off-state. (b) E-field distribution in GaN along the cutline shown in (a). The peak E-field is at the gate edge rather than near the fin bottom.

Fig. 11. Transfer curves of the fabricated vertical fin power FET with 200 nm channel width, at 25 Fig. 12. Output characteristics of a 10 A large °C and 150 °C. The left y-axis is in log scale with fin FETs. The device consists of over 600 fins the right y-axis in linear scale. The drain bias is with a channel width of ~250 nm in each fin. 1.5 V for this measurement.

Fig. 13. Off-state I-V characteristics of a 10-A-level large fin FET, with a breakdown voltage over 800 V. (Inset) Photo of the fabricated large device consisting of over 600 fins.

Fig. 14. Specific  $R_{\rm on}$  versus BV of the GaN vertical fin power FET, benchmarked with other normally-off lateral and vertical GaN transistors. Top point of this work represents the  $R_{\rm on}$  normalized with the total device area and the other point represents the  $R_{\rm on}$  normalized with the total fin area.

TABLE I. Summary and benchmark of device structures and key device metrics for the GaN vertical and lateral transistors with high current ratings reported.

|   | Device<br>Structure                 | $R_{on}$ $(m\Omega cm^2)$ | BV<br>(V) | V <sub>th</sub> (V) | I <sub>ON, SAT</sub> (A/cm <sup>2</sup> ) | I <sub>OFF</sub><br>@1200 V  | Large<br>Device    |

|---|-------------------------------------|---------------------------|-----------|---------------------|-------------------------------------------|------------------------------|--------------------|

| V | Fin FET<br>(This work)              | 0.2 (1.0)                 | 1200      | 1                   | 25000                                     | (A/cm²)<br><10 <sup>-4</sup> | 10 A /<br>800 V    |

|   | CAVET [3]                           | 2.2                       | 1500      | 0.5                 | 1500                                      | 0.02                         | 2.3 A /<br>1400 V  |

|   | Trench<br>CAVET [4]                 | 1.0                       | 1700      | 2.5                 | 3500                                      | 0.01                         | 15 A /<br>400 V    |

|   | Trench<br>MOSFET [5]                | 2.7                       | 1600      | 2                   | ~1100                                     | <10-8                        | 23.2 A /<br>1200 V |

| L | Gate Injector<br>Transistor<br>[13] | 2.3                       | 1250      | 3                   | 0.4<br>A/mm                               | 10 <sup>-7</sup><br>A/mm     | 10 A /<br>600 V    |

|   | Gate-recess<br>HEMT [11]            | 9                         | 1200      | 0.64                | 255                                       | 0.005                        | 5.5 A /<br>1200 V  |

Note: 'V' represent 'Vertical' and 'L' represent 'Lateral'.